Welcome !

Welcome to the YASEP.org website !

version PRELIMINARY

(several features are broken or under development)

What is the YASEP ?

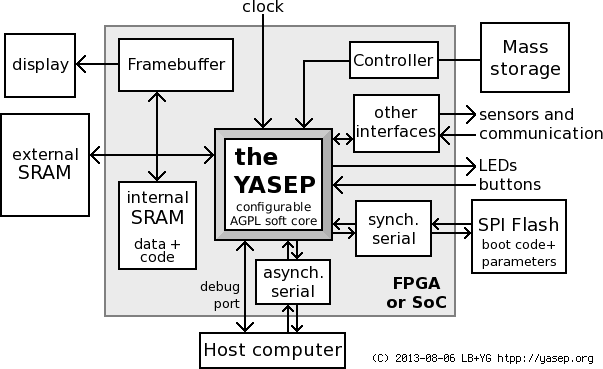

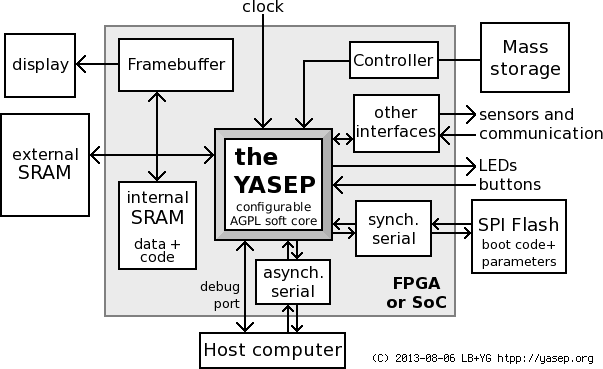

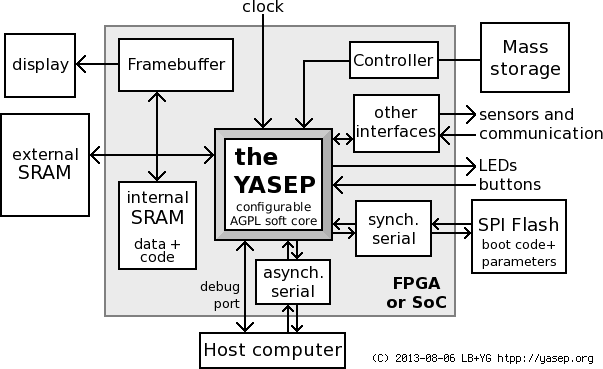

The acronym "YASEP" means "Yet Another Small Embedded Processor".

It's a family of original, Free,

configurable (16-bit or 32-bit) microcontroller cores,

meant to be quite small and as simple as possible (well, that's the original idea).

By choosing sometimes unusual methods, it is possible to concentrate on the real issues of CPU development

(mainly : architectural choices and implementation details).

The YASEP exists in the form of this website, which is not just

source code,

a

simulator, an

assembler,

a

disassembler,

a

manual, a

configuration tool, it is all that and it will be much more !

Every part is integrated in the others (and vice versa), so the whole remains (almost) coherent, easy to use and

quick to develop, fix and maintain.

Happy clicking !

yg

You read this message because there is an internal bug, you are a search engine, JavaScript

is disabled or your connection is too slow but most probably you don't use Firefox

or a capable enough web browser. Notably, old MSIE often fails. I'm so sorry ! I never meant

to give you up, to let you down, to run around and desert you...

The YASEP's features and characteristics

- Single-issue, pipelined, in-order, RISC architecture with 16 "registers" (including PC) and register-mapped memory.

- Orthogonal 16-bit instructions : about 40 opcodes with

an optional 16-bit additional immediate word or extended word

- Compact instruction words with short and long immediate, 2, 3 or 4 register operands.

- Configurable with either a 16 or 32-bit wide datapath

with/without several features (memory, multiply...).

- Register-mapped memory increases data memory bandwidth :

an instruction can trigger up to 3 data memory accesses, instead of 1 for a

typical load-store architecture.

- The abstract architecture is specified with JavaScript+HTML,

which generates the VHDL source code (suitable for FPGA and ASIC). Actel's ProASIC3

is the targeted technology, other brands will come later.

-

The YASEP is Free Hardware ! It is available under the Affero GPL license.

No patent (pending or known) applies to this core.

All the code is original and copyrighted by myself, no licensing fee is collected.

And your help is welcome :-)

Status

The microYASEP executed its first instructions in FPGA in 2012-03

and in JavaScript and VHDL simulation in 2012-11. The first Mandelbrot sets were computed in July 2013.

However the YASEP project is still not considered ready. The pointer update system is not yet developped.

Planned for 2013/2014 : GNL, compiler frontends (C, Pascal ?),

faster simulation, enhanced pointers... Stay tuned !

Download

You can download the whole YASEP website (source code, pages, documentation, tools, etc.) as

a single archive (about 510KB in .tar.bzip2). You can test the YASEP at home, and play

with the source code at will.

Note : if you want to use certain features

(like file save/load),

you need a web server with PHP on your computer. Install Apache under GNU/Linux,

or EasyPHP under MS Windows.

This site

The following open directories contain search-engine-friendly data ;-)

- ASM: Assembly language tools and interfaces

- core-js: the JavaScript source code of the YASEP definitions, assembler, disassembler, simulator...

- defora: several files (some automatically generated) to support

DeforaOS' assembler and disassembler

- dev: code for developping this site (minifier)

- doc: documentations about various aspects of the project

- examples: exemples de code source pour programmer le YASEP

- GNL: "GNL is Not a Language" (or my vision of a block-based programming interface)

- gui-js: the JavaScript source code of many interfaces and gadgets

- img: pictures, illustrations

- ISM: the Instruction Set Manual pages

- tracker: the bug & tasks tracker

- test: some proof of concept codes

- tuto: some tutorials

- C and VHDL source code are available again, enjoy :-)

The YASEP on the web

- The YASEP has its own website : yasep.org. You are probably reading this there.

- Some mirrors exist as well, and may be out of synch. The one at seul.org vanished in early 2010

due to technical problems, after 10 years of great service. Another mirror

is now available from TuxFamily. Thank you !

- Another mirror, courtesy of Troy

- The old versions of the site are kept separate in archives (for historical reasons).

- A blog provides less-technical informations and some human interaction.

- The YASEP is also on facebook

Other websites

- The Colibri is a little cost-effective FPGA module

(the successor of the FoxVHDL board without the VGA output). Among other things, it is ideal to develop and prototype the YASEP.

- I also helped to define the second version of this nice prototyping board.

- Trioflex has nifty FPGA boards ! The Stamp

(ST32PA3-AP8) is probably the tiniest, cheapest and smallest FPGA that the microYASEP can run on.

- One day, the YASEP will hopefully run on an Actuino board :-)

- A modular assembler (written in C) is being

developped by DeforaOS and support for the YASEP architecture started in september 2011.

- OpenCollector is the best place to look for other Free designs and tools !

- F-CPU is where it all started (more or less)

- Wikipedia has an interesting list of soft cores.

- The Homebuilt CPUs WebRing is maintained by Dave R Brooks

Browser requirements

This website has been designed with CPU efficiency and small memory footprint in mind

so it could work on embedded, handheld or cheap devices like the Raspberry Pi.

Supported web browsers

This site is developed on a basic laptop with Firefox

(currently 22, but 3.5 should work), plus some tests on Opera and Safari from time to time.

It is known to work with other browsers like Seamonkey, Omniweb, Shiira, Safari, Konqueror and Chrome. With a flaw or two.

It is known to not work well with Internet Explorer, however I have seen remarkable efforts since 2011

for the latest versions. It's welcome since supporting old IE

is counter-productive.

Camino seems to not like it either.

The site uses a lot of drag&drop, it does not work with "tablets" or "smartphones" (iPhone, iPad, Android...).

iPhone's Safari doesn't even load window's contents correctly.

Use a desktop or a laptop, with a mouse or a stylus, but touch surfaces don't do it...

Cookies

They are only used to add useful persistence for navigation

(language, window types and positions...). No user specific data are recorded, sent or used.

The site is mostly stateless and no session is handled by the server.

Save your work often !

Bienvenue !

Bienvenue sur le site de YASEP.org !

version PRÉLIMINAIRE

(quelques parties ne fonctionnent pas encore)

Qu'est-ce que le YASEP ?

L'acronyme YASEP signifie "Yet Another Small Embedded Processor"

(Encore Un Autre Petit Processeur Embarqué, mais "EUAPPE" sonne moins bien).

C'est une famille de microcontrôleurs paramétrables (16 ou 32 bits)

que j'ai imaginée en parallèle et souvent en contradiction avec le projet F-CPU.

Il est conçu pour être aussi petit et simple que possible (enfin, c'est l'idée initiale),

ce qui permet de le développer avec un minimum d'efforts et avec des ressources limitées.

En choisissant des méthodes parfois inhabituelles, il est possible de se concentrer

sur les véritables objectifs du développement d'un CPU (principalement : les choix

architecturaux et les détails d'implémentation).

Le YASEP existe sous la forme de ce site web. Ce n'est pas juste un simulateur,

un assembleur, un désassembleur,

un manuel ou un kit de développement,

c'est tout ça et bien plus encore ! Chaque partie est intégrée dans les autres

(et vice versa), l'ensemble reste donc (plutôt) cohérent, facile à utiliser,

à développer, à réparer, à maintenir...

Happy clicking !

yg

Caractéristiques du YASEP

-

Architecture RISC avec 16 registres (dont PC et mémoire).

-

Jeu d'instructions orthogonal sur 16 bits : environ 40 opcodes,

extensible avec un champ immédiat de 16 bits ou un champ étendu.

-

Instructions avec champ immédiat long ou court et 2, 3 ou 4 registres.

-

Chemin de donnée à largeur configurable (16 ou 32 bits),

indépendant des instructions, avec ou sans de nombreuses options (mémoire, multiplication...).

- L'accès à la mémoire au travers des registres optimise la bande passante :

une instruction peut déclencher jusqu'à 3 accès à la mémoire, au lieu d'un seul pour les architectures "load-store" typiques.

-

L'architecture abstraite est spécifiée en JavaScript+HTML,

dont est dérivé le code source en VHDL (compatible FPGA et ASIC).

La technologie cible est le ProASIC3 de Actel, d'autres familles suivront plus tard.

-

Le YASEP est libre et gratuit ! Aucun brevet (déposé ou connu) ne concerne le cœur.

Tout le code source est original et distribué sous license CopyLeft

(Affero GPLv3). Toute aide est la bienvenue :-)

Statut

Le microYASEP a exécuté ses premières instructions dans un FPGA en mars 2012,

et calculé ses premiers ensembles de Mandelbrot en juillet 2013.

Cependant le projet n'est pas considéré comme prêt, il manque encore la gestion automatique des pointeurs.

Prévus pour 2013/2014 : progresser sur GNL, accélérer les simulations,

compiler du C et/ou du Pascal, gestion des pointeurs...

Téléchargez-moi !

L'ensemble de ce site est disponible dans une archive

(environ 510KB au format .tar.bzip2) pour l'utilisation en local.

Vous pouvez tester le YASEP chez vous et jouer avec le code source comme il vous chante.

Note : si vous souhaitez utiliser la fonction de sauvegarde/chargement de fichiers de FileFox,

vous aurez besoin d'un serveur web avec PHP sur votre ordinateur. Installez Apache sous GNU/Linux,

ou EasyPHP sous MS Windows.

Sur ce site

Nos amis les moteurs de recherche peuvent se régaler dans ces répertoires ouverts ;-)

- ASM: outils pour l'assembleur et les interfaces de programmation

- core-js: Le code source JavaScript du YASEP avec les définitions,

l'assembleur, le désassembleur, le (futur) simulateur...

- defora: des fichiers (certains générés automatiquement)

pour l'assembleur et désassembleur de DeforaOS

- dev: code pour développer ce site (minifieur de page web)

- doc: documentations du projet

- examples: exemples de code source pour programmer le YASEP

- GNL: "GNL is Not a Language" (ou ma vision d'une interface graphique pour développer du code)

- gui-js: le code source en JavaScript de nombreuses interfaces et gadgets, dont le gestionnaire de fenêtres

- img: images, illustrations

- ISM: les pages du Manuel du Jeu d'Instructions (Instruction Set Manual)

- test: quelques bricolages

- tracker: le gestionnaire de bugs et de tâches

- tuto: quelques tutoriels

- C et VHDL : encore plus de code source :-)

Le YASEP sur le web

- Le YASEP a son propre site web : yasep.org. Vous lisez probablement ce texte sur ce site.

- Quelques miroirs existent aussi, et sont probablement désynchronisés. Celui à seul.org

a disparu début 2010 après 10 ans de bons et loyaux services après des soucis techniques.

- Un nouveau miroir est maintenant disponible chez TuxFamily. Merci !

- Un autre miroir, hébergé par Troy

- Les anciennes version du site sont gardées en archives pour des raisons historiques.

- Un blog distille des informations techniques et livre quelques perspectives sur le projet.

- Le YASEP est aussi sur facebook

D'autres sites web

- Le Colibri est un petit module FPGA économique (successeur

de la carte FoxVHDL) idéal pour prototyper le YASEP (parmi d'autres choses)

- J'ai aussi participé à définir la version 2 de cette carte de prototypage

- Trioflex a aussi des cartes FPGA sympathiques. La Stamp

(ST32PA3-AP8) est probablement le FPGA le plus petit et le plus économique sur lequel le microYASEP peut tourner.

- Un jour, le YASEP tournera sur une carte Actuino :-)

- Un assembleur modulaire (écrit en C)

est en cours de développement par DeforaOS et le support du YASEP a commencé en septembre 2011.

- OpenCollector est le meilleur site pour les outils et projets de Hardware Libre !

- F-CPU : c'est là que tout a commencé (plus ou moins)

- Wikipedia a une bonne liste de "soft cores".

- Le Homebuilt CPUs WebRing est maintenu par Dave R Brooks

Configuration du navigateur

Ce site web a été conçu avec le souci de l'efficacité, en n'utilisant que le minimum

de ressources de processeur et de mémoire, afin qu'il puisse fonctionner sur des appareils

embarqués, portables ou économiques comme le Raspberry Pi.

Navigateurs supportés

Ce site est développé sur un bête petit laptop avec GNU nano et Firefox

(version 22 actuellement mais 3.5 devrait fonctionner). J'effectue

des tests sur Opera et Safari de temps en temps.

Il fonctionne assez bien sur Seamonkey, Omniweb, Shiira, Safari, Konqueror et Chrome, avec un défaut ou deux...

Internet Explorer n'aime pas trop ce site, bien que les toutes dernières versions de MSIE

aient fait des progrès remarquables depuis 2011. C'est bienvenu car supporter les vieilles versions

serait contre-productif.

Camino n'aime pas.

Le site utilise beaucoup de drag&drop, il fonctionne mal avec les "tablettes"

ou les "smartphones" (iPhone, iPad, Android...).

D'ailleurs le Safari de l'iPhone n'arrive même pas à charger le contenu des fenêtre externes.

Utilisez un vrai PC ou un laptop, avec une souris, un trackpad ou un stylet, mais

les surfaces tactiles ne conviennent pas.

Cookies

Ils servent uniquement à ajouter de la persistence pour la navigation

(langue, type et position des fenêtres...). Aucune donnée n'est enregistrée, lue

ou utilisée par le serveur. Ce site ne dispose pas de session, donc pensez à sauvegarder

votre travail souvent !