Le microYASEP est un sous-ensemble minimal du YASEP, destiné aux applications qui font habituellement appel à des microcontrôleurs économiques. Il est optimisé pour une taille minimale et devrait tenir dans un petit FPGA, ce qui permet de remplacer des puces du commerce (on ne trouve jamais de modèle qui convient parfaitement au niveau brochage, fonctionalités ou performance). La partie FPGA, accédée au travers des Registres Spéciaux, gère les opérations rapides ou dédiées en temps réel alors que le YASEP gère le fonctionnement du système en tâche de fond. Comme le YASEP est intégré au FPGA, les coûts et l'empreinte sur le circuit imprimé sont réduits. De plus, les fonctionalités du YASEP peuvent être adaptées très précisément à l'application, pour n'utiliser que le strict nécessaire, et cela résoud les problèmes de communication courants : pas besoin d'interface compliquée, de broche, de SPI ou de protocole, les signaux internes sont connectés directement. Le logiciel en est grandement simplifié.

Les contraintes de départ sont les suivantes :Par contre, en bonus, il est possible d'adresser 16 broches ou signaux internes pour en faire des conditions (plus que le RCA1802 ;-D).

Comme de nombreux microcontrôleurs, le microYASEP divise sa mémoire en deux, avec une banque pour les données et une autre pour les instructions. Une mémoire unifiée serait possible mais cela dépend de la technologie utilisée (le microYASEP exploite les mémoire double port disponibles dans les FPGA).

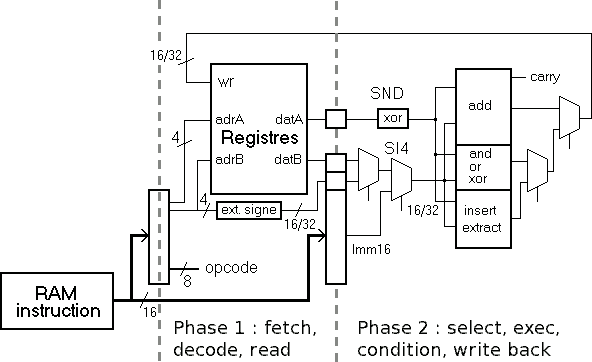

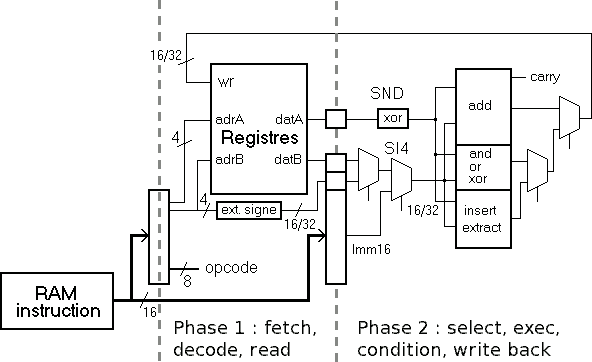

La mémoire instructions, sur 16 bits, fournit un demi-mot à chaque cycle d'horloge. Comme une instruction peut s'étaler sur deux demis-mots, le microYASEP exécute toujours une instruction en deux cycles d'horloge. Le format des instructions est conçu pour permettre un maximum de réutilisation de la logique de décodage. Le premier mot fournit toutes les informations nécessaires pour démarrer l'exécution, en parallèle de la lecture du demi-mot suivant.

Dans cette version, le temps d'accès de la mémoire est supposé presque instantané, une fraction de la période d'horloge (quelques nanosecondes pour une SRAM de FPGA). Il n'y a donc pas de pipeline et les sauts sonts immédiats, sans nécessiter de "delay slot" ou de cycle mort.

Pour les cas où la mémoire disponible est très faible, les registres sont câblés avec des portes logiques. Cela économise deux blocs de SRAM, ce qui permet de disposer de plus de place pour les instructions et les données sur la puce. Par contre, cela prend beaucoup plus de place et d'énergie, et c'est lent...

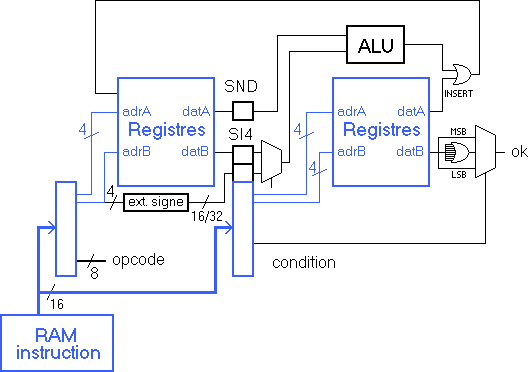

Il y a 16 registres, connectés au chemin de données par deux gros multiplexeurs, ce qui permet de lire deux opérandes par cycle. Comme une instruction s'exécute en deux cycles, le microYASEP peut lire 4 opérandes par instruction : deux lors de la première phase (SND et SI4), deux dans la deuxième (une condition et une donnée auxiliaire DST pour certaines instructions).

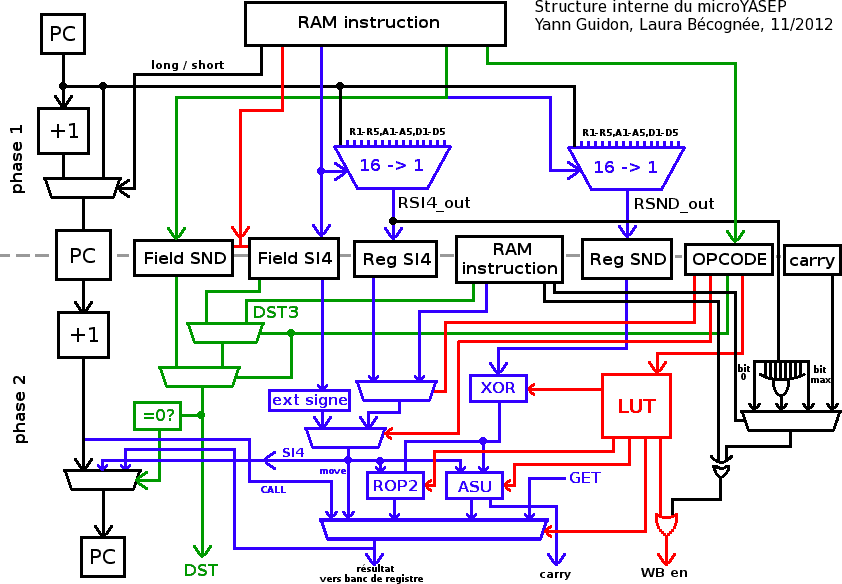

Le code source VHDL tient sur environ 360 lignes. Il est dérivé du diagramme suivant :

Légende (de gauche à droite):

La version 16 bits tourne à approximatevement 20 MIPS sur un A3P060 (FPGA à cellules Flash).