Dans les exemples suivants, nous considérons que nous effectuons un

décalage de deux positions, soit une division par 2^2=4.

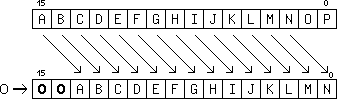

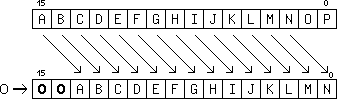

Pour un YASEP16, le mouvement des bits peut être schématisé ainsi :

Pour YASEP32 c'est identique, mais avec 32 bits au lieu de 16.

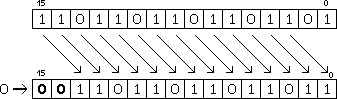

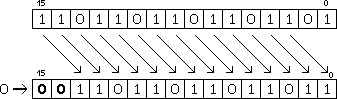

Supposons que le registre R1

est chargé avec la valeur 1101101101101101b, soit 56173 en décimal.

L'opération de décalage non signé peut être écrite ainsi

mov 1101101101101101b r1

shr 2 r1

56173/4=14043, ce qui correspond au résultat binaire 11011011011011b.