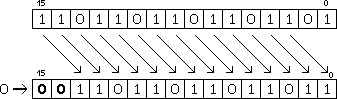

Let's consider that R1 gets loaded with 1101101101101101b, or 56173 in decimal. The unsigned shifting operation can be written this way:

mov 1101101101101101b r1 shr 2 r156173/4=14043, which is equal to the binary result 11011011011011b.

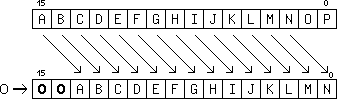

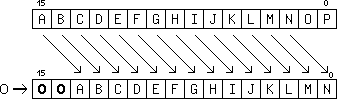

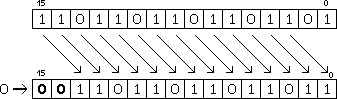

The bits of the source register (snd) are shifted towards the LSB, by a number of bits indicated either by

The MSB of the result are filled with 0s for this logic shift, while the arithmetic shift (SAR) fills the MSB with the value of the original MSB.

Let's consider that R1 gets loaded with 1101101101101101b, or 56173 in decimal. The unsigned shifting operation can be written this way:

mov 1101101101101101b r1 shr 2 r156173/4=14043, which is equal to the binary result 11011011011011b.