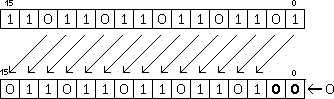

Let's consider that R1 gets loaded with 0110110110110110b, or 28086 in decimal. The left shifting operation can be written this way:

mov 0110110110110110b r1 shl 2 r128086*4=112444, which does not fit in the register (limited to 65535) so the result is truncated and we get 112444%65536=46808=1011011011011000b

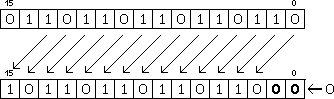

The sign of the result can change, if we consider signed integers, such as -9363, written 1101101101101101b in binary: