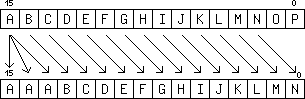

Supposons que le registre R1 est chargé avec la valeur 0110110110110110b, soit 28086 en décimal. L'opération de décalage signée peut être écrite ainsi

mov 0110110110110110b r1 sar 2 r128086/4=7021, ce qui correspond au résultat binaire 0001101101101101b.

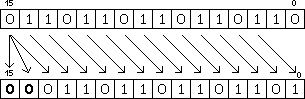

Contrairement à SHR cette instruction préserve le bit de signe si on travaille avec des nombres entiers signés. Par exemple avec la valeur 1101101101101101b, qui correspond à -9363, le décalage signé donne ce résultat :

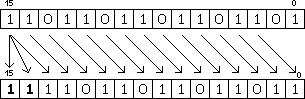

Le décalage à droite arrondit à l'excès pour les nombres négatifs, mais SAR ne sert pas qu'aux divisions.