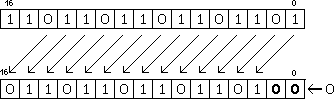

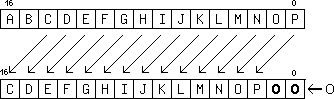

Supposons que le registre R1 est chargé avec la valeur 0110110110110110b, soit 28086 en décimal. L'opération de décalage à gauche peut être écrite ainsi

mov 0110110110110110b r1 shl 2 r128086*4=112444, ce qui ne tient pas dans un registre 16 bits (limité à 65535) donc le résultat est tronqué et nous obtenons 112444%65536=46808=1011011011011000b

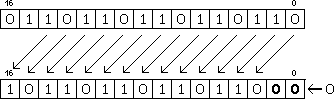

Le signe du résultat peut changer, si on considère des entiers signés, comme dans le cas de -9363, écrit 1101101101101101b en binaire :