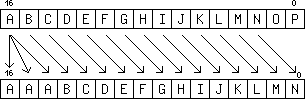

Let's consider that R1 gets loaded with 0110110110110110b, or 28086 in decimal. The unsigned shifting operation can be written this way:

mov 0110110110110110b r1 shr 2 r128086/4=7021, which is equal to the binary result 0001101101101101b.

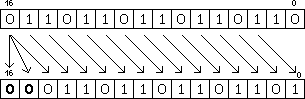

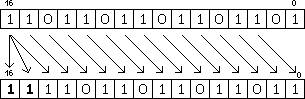

Unlike SHR, this instruction preserves the sign bit when we work with signed integers. For example with the value -9363, written 1101101101101101b in binary, we get this result:

Indeed, right signed shifts round up for the negative numbers, but SAR is useful for more than these kinds of divisions.