"Ne pas céder à l'intimidation, qui n'est que le premier pas vers le renoncement civique et l'abdication de la liberté tout court."

"L'abeille et l'économiste"

par Yann Moulier Boutang, 2010, page 28

"Intel

Active

Management Technology (AMT) is hardware-based technology for remotely managing

and securing PCs out-of-band."

http://www.uberwall.org/bin/download/download/102/lacon12_intel_amt.pdf:

Non désactivable, mot de passe par défaut et envoyés en clair sur le réseau...

Même éteint !

MIPS : 82 brevets "essentiels"

(plus 498 vendus à Allied Security Trust, "non practicing entity")

Intel, IBM, SUN/Oracle...

ARM : http://whitequark.org/blog/2012/09/25/why-raspberry-pi-is-unsuitable-for-education/

Smartphone : "There are over 250,000 patents and 5 million claims at play inside your pocket."

"Il ne peut y avoir de logiciel libre sans matériel libre"

Pourquoi le YASEP ?

joindre l'utile à l'agréable

Pourquoi cette conférence ?

aller au contact des utilisateurs

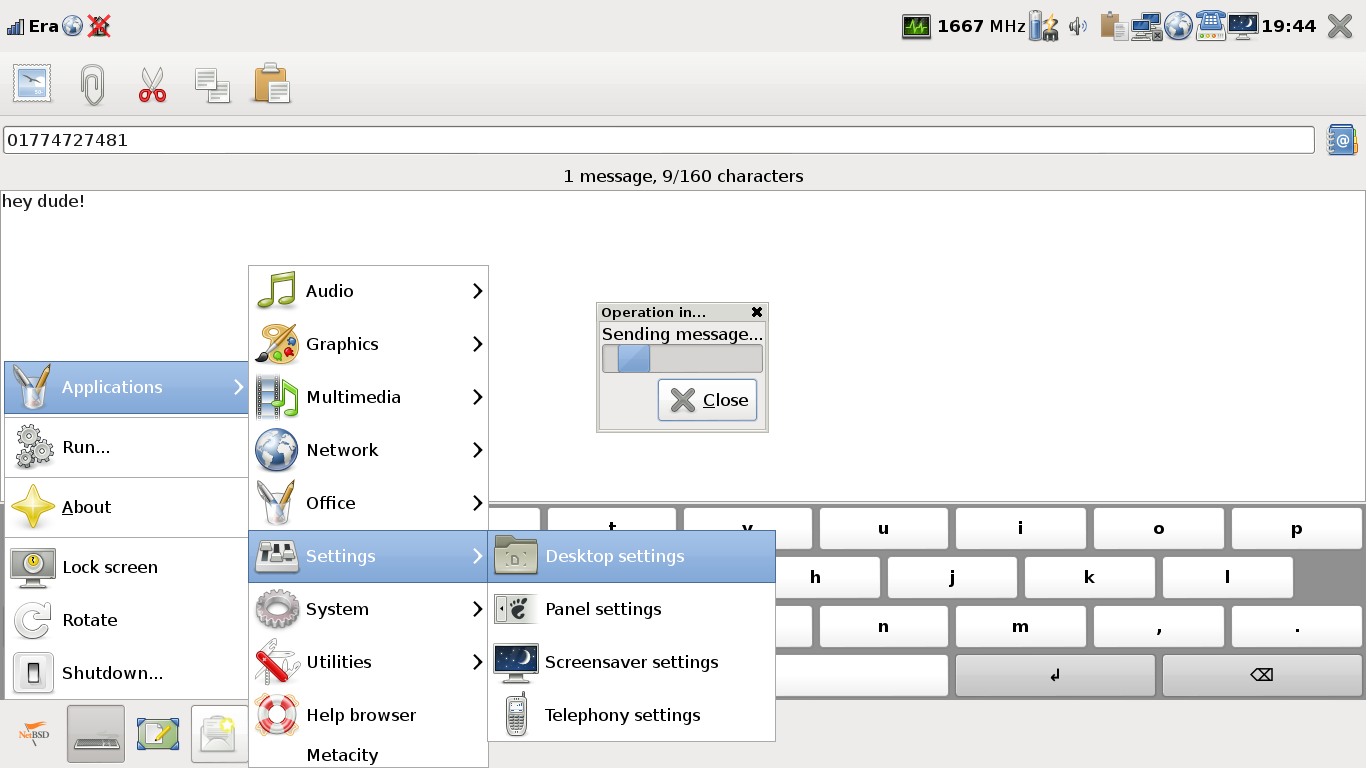

outils JavaScripts (programmation, debug & configuration)

intégrés dans un window manager

Bientôt (décembre 2012) :

Ensuite (2013-2014) :

Futur :

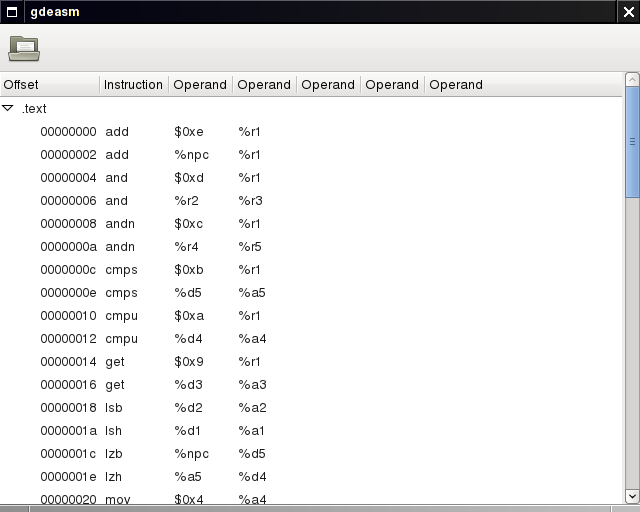

L'assembleur de Defora supporte

les architectures :

L'assembleur de Defora supporte

les architectures :

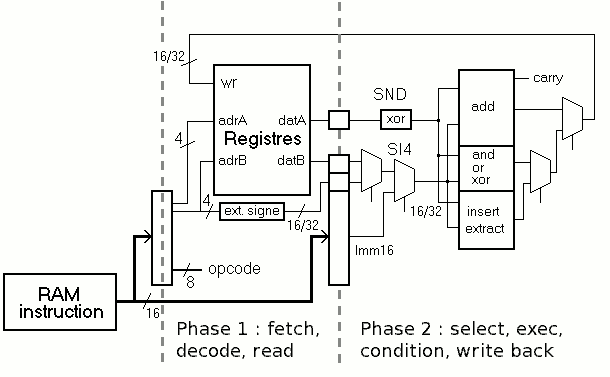

- Type RISC "compact"

- Instructions simples et orthogonales

- Tous les opcodes sont conditionnel

- 16 registres accessibles

- Pas d'instruction de saut (JMP/branch)

- Pas de load/store : Register-mapped memory

(La destination est écrite en dernier.)

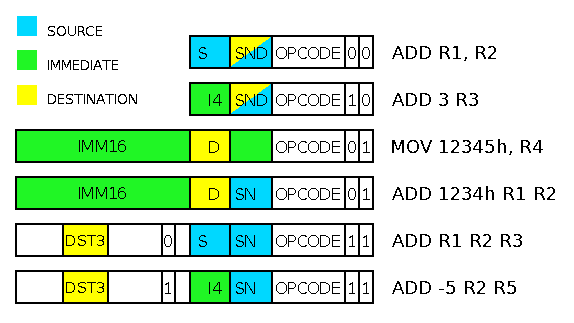

ADD R2,R1

ADD R2,R1R1 <= R1 + R2

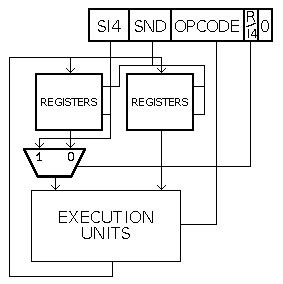

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src/Imm4 | src/dest | opcode | Reg | court | |||||||||||

| R2 | R1 | ADD | 0 | 0 | |||||||||||

ADD [-8..7],R1

R1 <= R1 + imm4

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src/Imm4 | src/dest | opcode | Imm4 | court | |||||||||||

| 2 | R1 | ADD | 1 | 0 | |||||||||||

Légende:

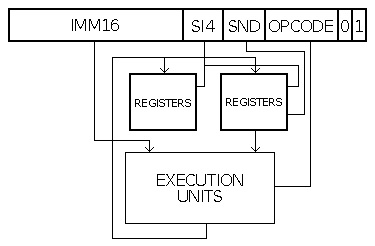

ADD R2,[-32768..32767],R1

R1 <= R2 + Imm16

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Imm16 | src/Imm4 | src/dest | opcode | Imm16 | long | ||||||||||||||||||||||||||

| 12345 | R2 | R1 | ADD | 0 | 1 | ||||||||||||||||||||||||||

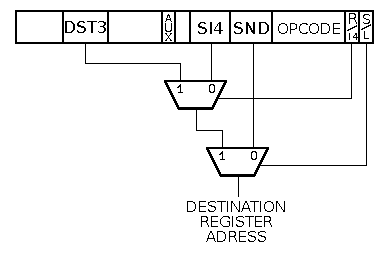

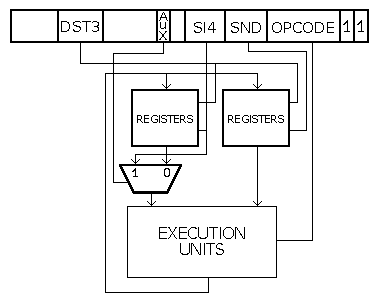

R3 <= R1 + R2

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| dest3 | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||||

| R3 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

R3 <= R1 + Imm4

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| dest3 | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||||

| R3 | 1 | 5 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

Auto-update de pointeurs ou opérandes :

ADD R1+ R2,R3R3 <= R1 + R2, R1 <= R1 + 1

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| dest3 | update | Reg | u | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||

| R3 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

| 00 | pas de mise à jour |

| 01 | post-incrémente |

| 10 | prédécrémente |

| 11 | post-incrémente |

4 bits disponibles pour

mettre à jour src/dest et dest3

À mettre au point en 2013

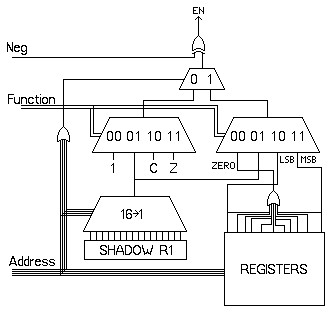

Si R4 est pair alors R3 <= R1 + R2

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src cond | dest3 | cond | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||

| R4 | R3 | LSB0 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||

| NZ (not zéro) | Z (Zéro) |

| Bit set R1 | bit clear R1 |

| LSB1 (impair) | LSB0 (pair) |

| MSB1 (negatif) | MSB0 (positif) |

| Always | Never |

| Carry | NoCarry |

| Zero | Not zero |

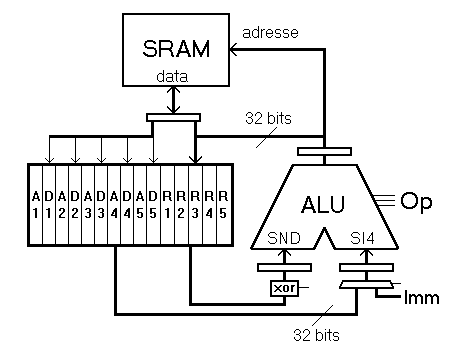

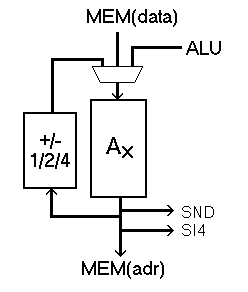

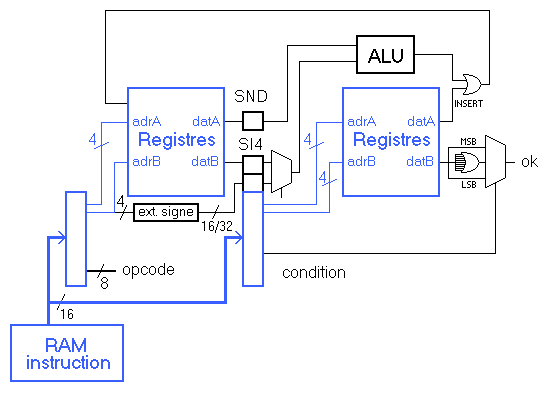

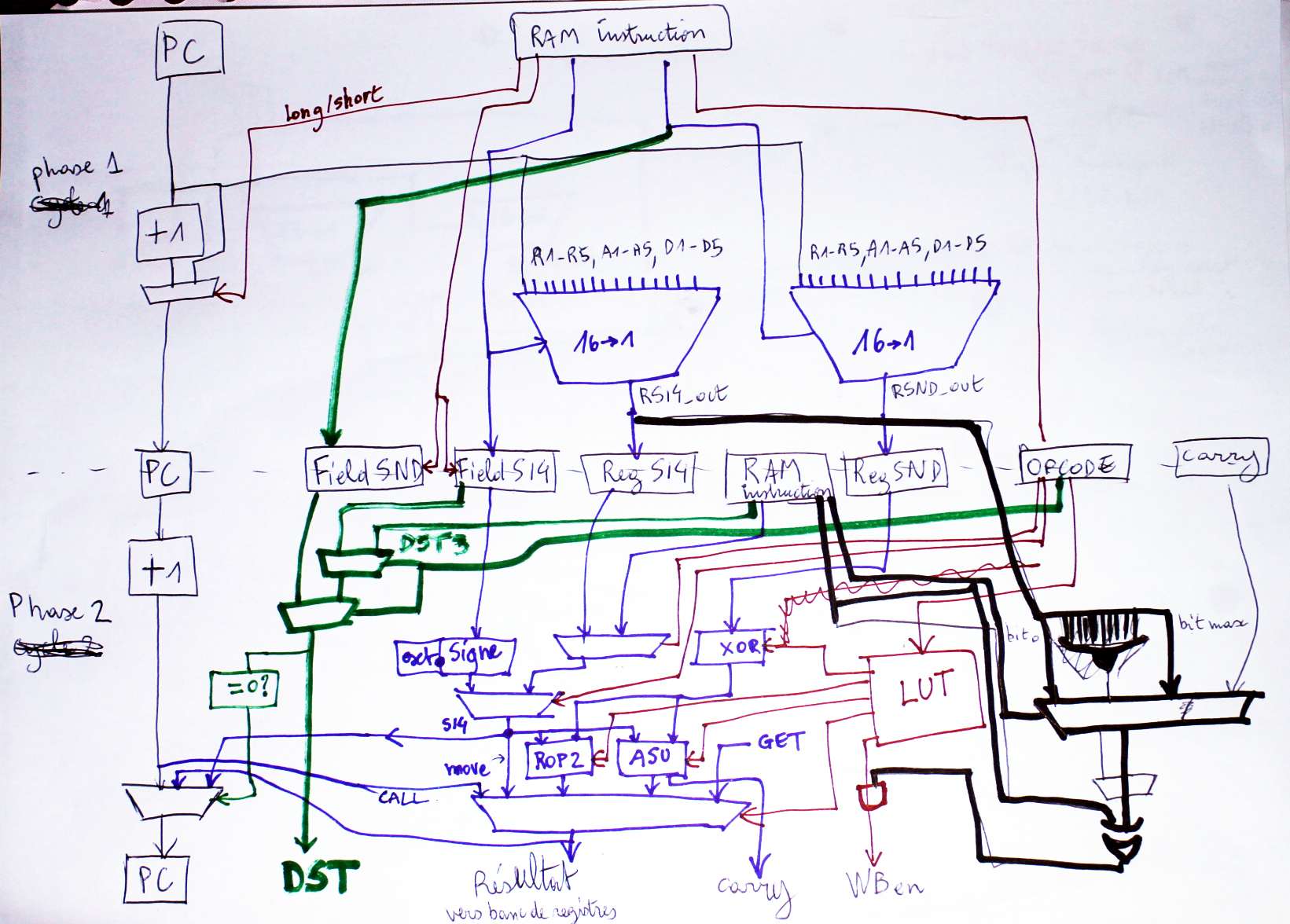

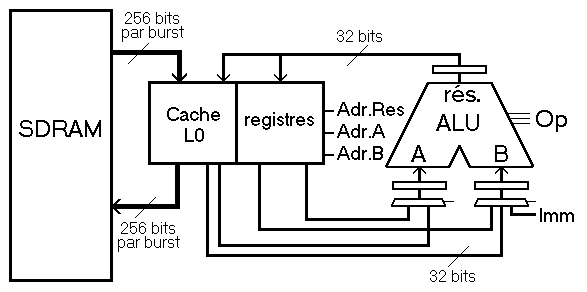

La mémoire est accédée en 2 phases au travers de 5 paires de registres : A1-D1, A2-D2, A3-D3, A4-D4, A5-D5 : on pointe et on tire !

Avantages : améliore la performance et la sécurité.

Lecture :mov 1234h A1 ; initialise l'adresse à 1234h mov D1 R1 ; recopie le contenu de la mémoire dans R1

Écriture :

mov 1234h A1 ; initialise l'adresse à 1234h mov R1 D1 ; écrit R1 dans la mémoire

Lorsqu'un accès sort d'un mot, le flag de retenue est mis à 1.

; (ce qui suit un point-virgule est un commentaire) ; Description: Juste un bête programme qui boucle ; en additionnant les nombres entiers de 1 à 10 .name MonPremierProgramme .profile YASEP16 mov 10 R1 ; initialise le compteur ; dans le registre R1, pour boucler 10 fois mov 0 R2 ; l'accumulateur est dans le ; registre R2, on le met à zéro ; corps de la boucle, tient dans 4 octets : add R1 R2 ; accumule le contenu de R1 dans R2 add -1 R1 ; décrémente le compteur add -4 PC NZ R1 ; reboucle tant que R1 n'a pas atteint zéro ; (soustrait 4 au compteur de programme, ; ce qui saute au début du corps de la boucle) HALT ; fin du programme : ; HALT est une instruction qui bloque le CPU

Partie 2

L'architecture etles principes du

YASEP

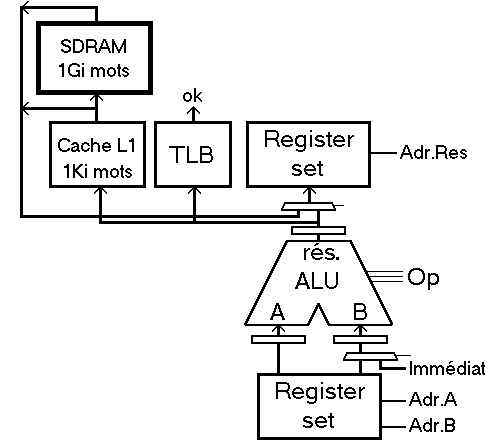

=> architecture "no load/store".

| #0: | PC | 1 PC |

| #1: | R1 | 5 registres normaux |

| #2: | R2 | |

| #3: | R3 | |

| #4: | R4 | |

| #5: | R5 | |

| #6: | D5 |

5 registres de données : accèdent directement aux buffers

5 registres d'adresse : |

| #7: | A5 | |

| #8: | D4 | |

| #9: | A4 | |

| #10: | D3 | |

| #11: | A3 | |

| #12: | D2 | |

| #13: | A2 | |

| #14: | D1 | |

| #15: | A1 |