and friends : Pierre Pronchery (DEFORA),

Laura (YGLLO), Troy (q3u.be) ...

And you ?

- A small embedded microprocessor

(hence the name : "Yet Another Small Embedded Processor" )

Don't forget the "the" - A website : http://yasep.org

- A CPU design framework

- A software development environment

- mid-2002 : The YASEP started as the "VSP" (Very Simple Processor), a side project. Happy birthday !

- dec. 2002 : 19C3@Berlin : last major F-CPU presentation.

- 2003-2007 : F-CPU stalls, VSP slowly becomes the YASEP and turns into my main hobby

- YASEP2009 : things get more serious and more organised

- YASEP2011 : reboot of the website around YGWM

- YASEP2013 : Starting next week

- Because I need it

- Because it must be better if I do it myself ;-)

- Because it's instructive and fun !

- Because it's possible

- Because it addresses many shortcomings of the F-CPU project

- Because it can also be useful to others

- Because new computing paradigms are necessary

- Because soon it will be too late !

« There can be no Free Software without Free Hardware »

In 2012, can you buy any new computer, install F/LOSS on it and/or keep it safe and under total control ?

=> MS owns your computer

Hackers and governments will 0wn your PC too, even when it's "off".

MIPS : 82 "essential" patents

(plus 498 sold to Allied Security Trust, "non practicing entity")

Intel, IBM, SUN/Oracle...

ARM : http://whitequark.org/blog/2012/09/25/why-raspberry-pi-is-unsuitable-for-education/

Smartphone : "There are over 250,000 patents and 5 million claims at play inside your pocket."

Can a microprocessor be successful and not encumbered by patents ? SPARC : LEON & OpenSPARC

- Quick & dirty development.

Nobody is looking at the code anyway. Come on. - New, "toy" architecture : the actual architecture does not matter anymore (in the world of SoC, I/Os prevail and SW is recompiled)

- Emphasis on usefulness, ease and simplicity

- Performance is pointless if it does not work

- Not tied to the GNU Compiler Collection (new paradigms)

- Slow maturation process, no rush, create a clean base

"don't hesitate to break often and rebuild better" - Holistic approach (software AND hardware)

- FUN

so it's « quite coherent »

JavaScript tools integrated in a window manager

As of 2012/12 :

What's expected :

(end of "submarine mode": presentations and workshops)

And a working tasks tracker...

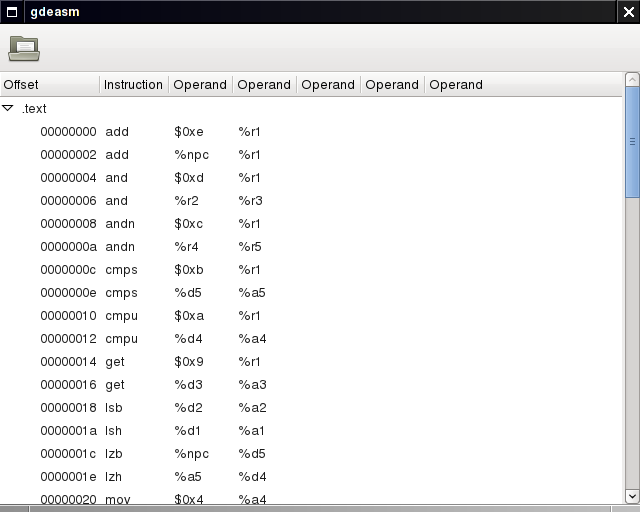

DeforaOS's assembler supports:

DeforaOS's assembler supports:

Microkernel based on BSD?

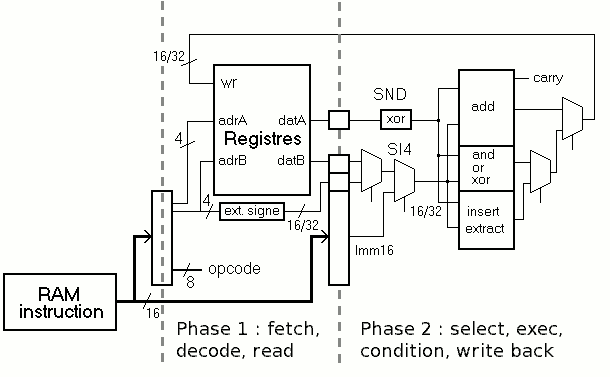

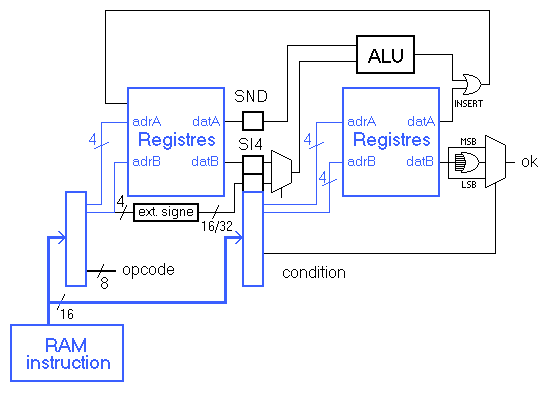

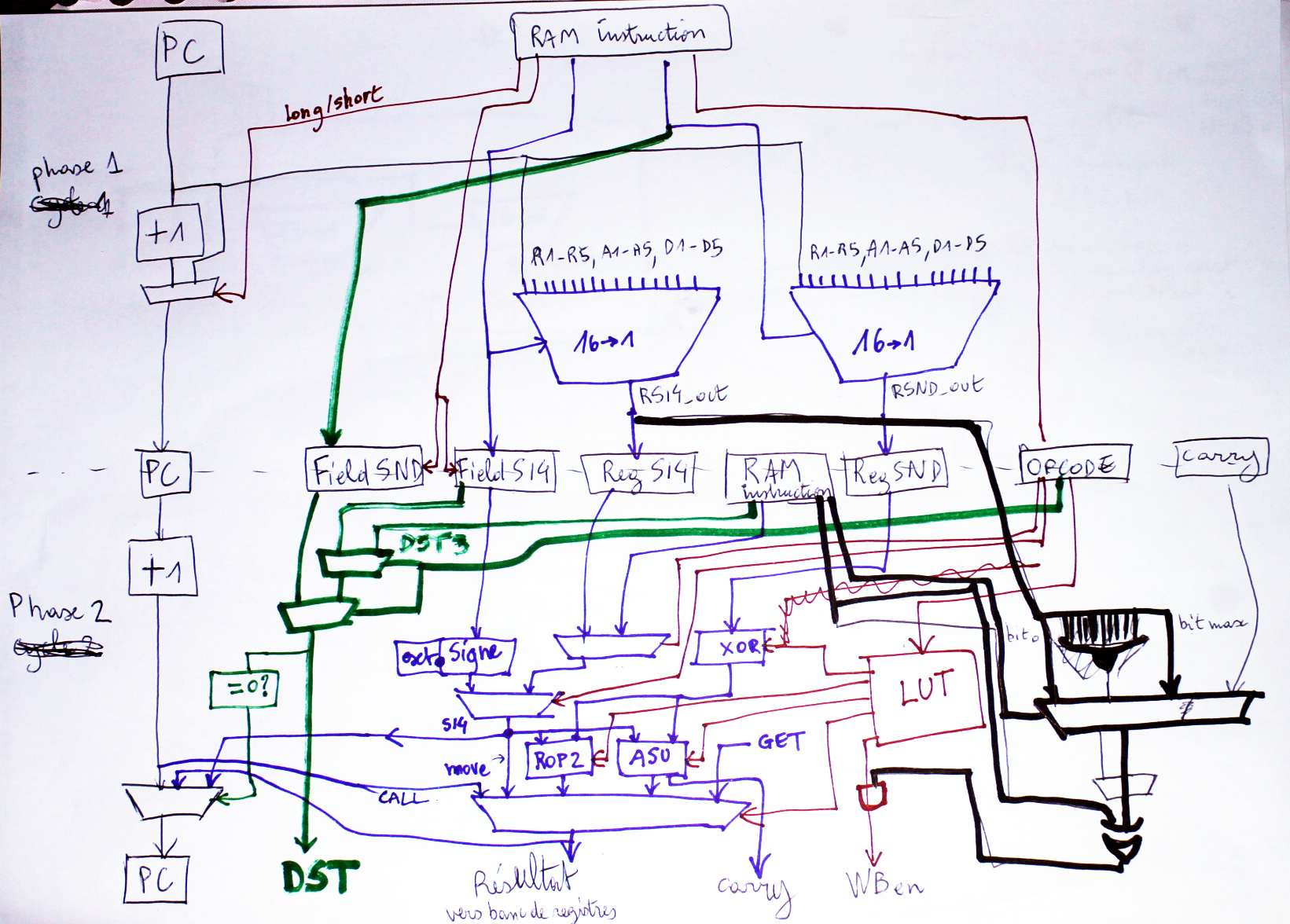

The YASEP's programming model :

- "Compacted" RISC (inspired by CDC6600)

- Simple and orthogonal instructions

Most opcodes can use all the operand combinations - All the opcodes can be predicated

- 16 registers

- No JMP/branch instruction (use the PC register instead)

- No load/store : Register-mapped memory

(The destination register is always written last.)

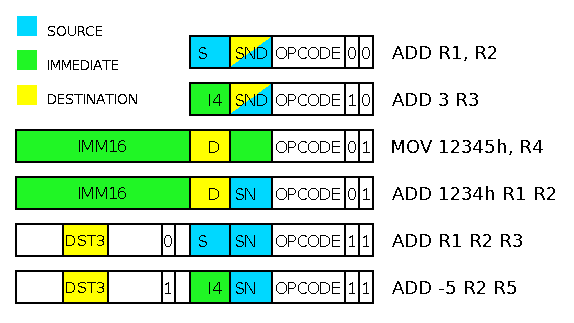

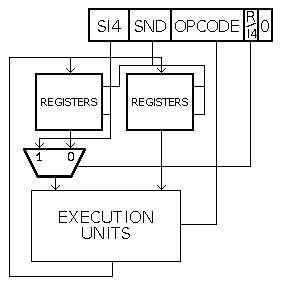

ADD R2,R1

ADD R2,R1R1 <= R1 + R2

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src/Imm4 | src/dest | opcode | Reg | court | |||||||||||

| R2 | R1 | ADD | 0 | 0 | |||||||||||

ADD [-8..7],R1

R1 <= R1 + imm4

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src/Imm4 | src/dest | opcode | Imm4 | court | |||||||||||

| 2 | R1 | ADD | 1 | 0 | |||||||||||

Legend:

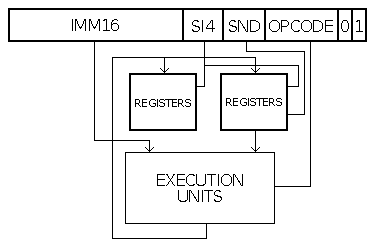

ADD R2,[-32768..32767],R1

R1 <= R2 + Imm16

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Imm16 | src/Imm4 | src/dest | opcode | Imm16 | long | ||||||||||||||||||||||||||

| 12345 | R2 | R1 | ADD | 0 | 1 | ||||||||||||||||||||||||||

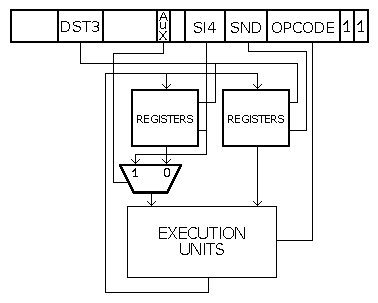

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

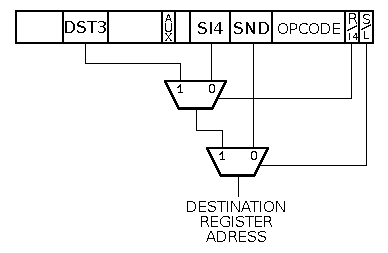

| dest3 | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||||

| R3 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| dest3 | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||||

| R3 | 1 | 5 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

Ifi R4 is even the R3 <= R1 + R2

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| src cond | dest3 | cond | Reg | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||

| R4 | R3 | LSB0 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||

| NZ (register is Not Zero) | Z (register is Zero) |

| Bit set R1 | bit clear R1 |

| LSB1 (odd) | LSB0 (even) |

| MSB1 (negative) | MSB0 (positive) |

| Always | Never |

| Carry | NoCarry |

| Zero | Not zero |

ADD R1+ R2,R3

R3 <= R1 + R2, R1 <= R1 + 1

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| dest3 | update | Reg | u | src/Imm4 | src/dest | opcode | Ext | long | |||||||||||||||||||||||

| R3 | 0 | R2 | R1 | ADD | 1 | 1 | |||||||||||||||||||||||||

| 00 | no update |

| 01 | post-increment |

| 10 | pre-decrement |

| 11 | post-increment |

4 bits are available to

modify src/dest and/or dest3

To be defined in 2013

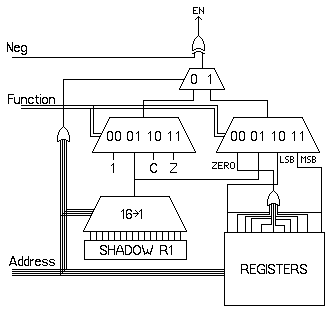

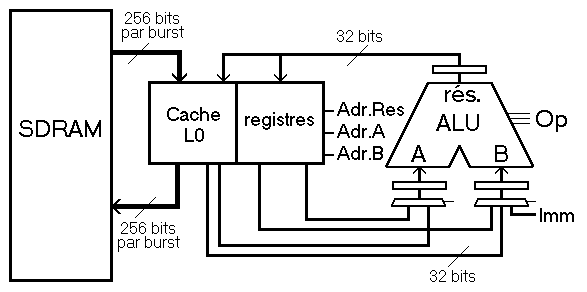

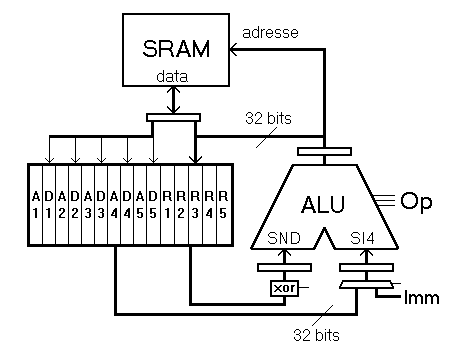

The memory is accessed in 2 phases through 5 register pairs: A1-D1, A2-D2, A3-D3, A4-D4, A5-D5 (« Point and shoot »)

Better performance, scalability and security than Load/store CPUs

Read :mov 1234h A1 ; point to address 1234h mov D1 R1 ; copy the memory contents into R1

Write :

mov 1234h A1 ; point to address 1234h mov R1 D1 ; write R1 to mémoire

Out-of-word half-word accesses set the carry flag.

The microYASEP :

- Simple subset of the YASEP,

a first implementation with less instructions, dumb memory - Useful for microcontroller tasks

when you don't want to use a M0, PIC or AVR... - Synthesised to 20 MIPS with little tuning on Actel

when flexibility (not performance) matters - Targets cheap FPGAs

http://www.mirifica.it/store/68-trioflex-st32pa3-ap8.html

http://www.mirifica.it/store/68-trioflex-st32pa3-ap8.html

A3P060 is the cheapest and smallest possible target (4 SRAM blocks = 2KB)

http://www.acmesystems.it/COLIBRI250

http://www.acmesystems.it/COLIBRI250A3P250 in BGA256 brings 32*256K=1MB of external SRAM, enough for a nice YASEP32

=> "no load/store" architecture.

| #0: | PC | 1 PC |

| #1: | R1 | 5 normal registers |

| #2: | R2 | |

| #3: | R3 | |

| #4: | R4 | |

| #5: | R5 | |

| #6: | D5 |

5 data registers: directlty access the buffers

5 address registers: |

| #7: | A5 | |

| #8: | D4 | |

| #9: | A4 | |

| #10: | D3 | |

| #11: | A3 | |

| #12: | D2 | |

| #13: | A2 | |

| #14: | D1 | |

| #15: | A1 |

no buffer or aliasing detection,

much smaller to fit in cheap FPGAs